# Cykle maszynowe

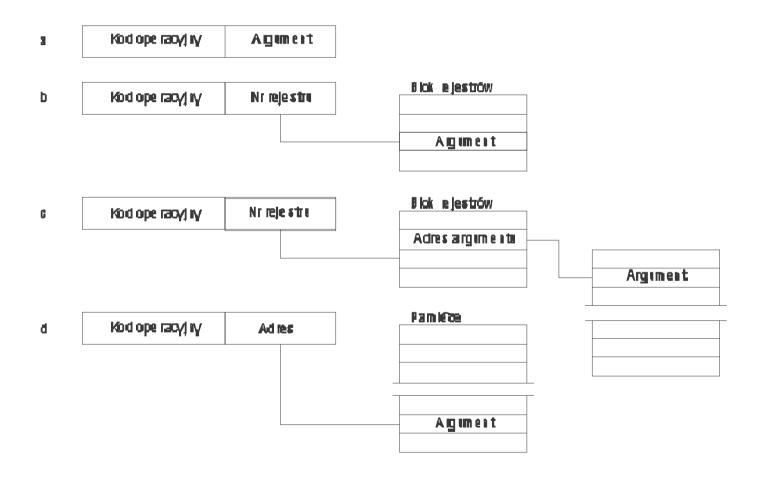

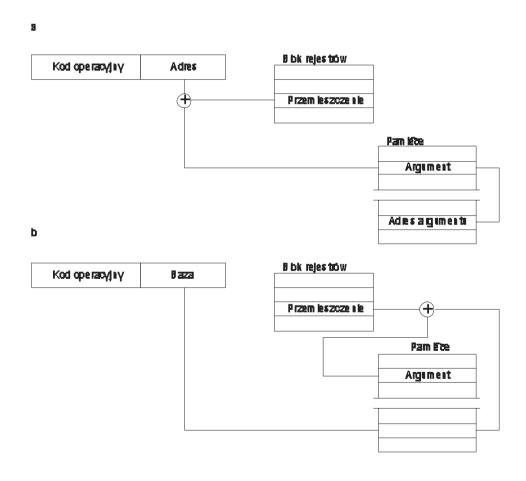

## Tryby adresowania

# Złożone tryby adresowania

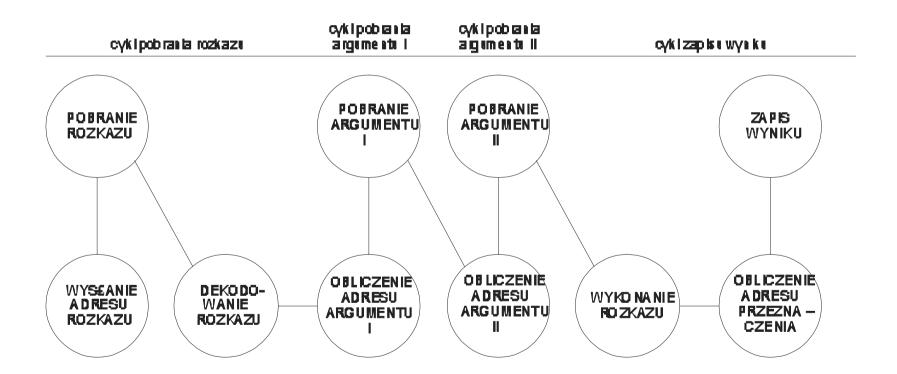

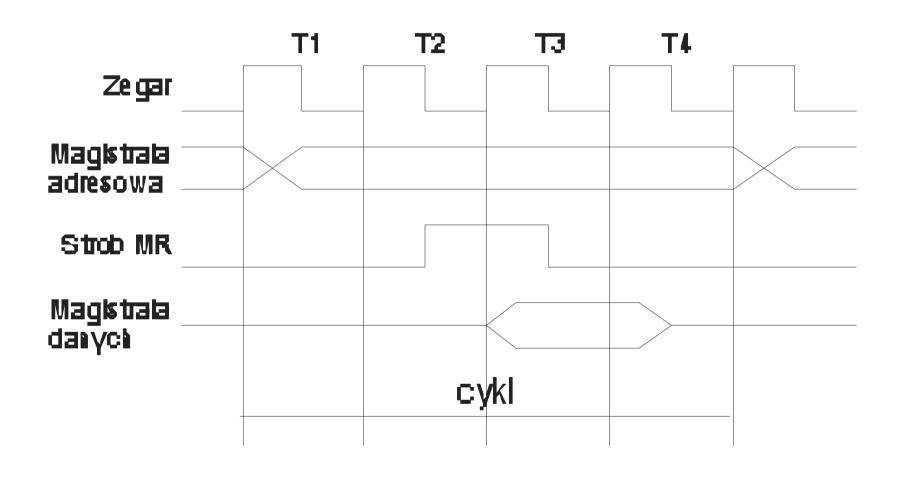

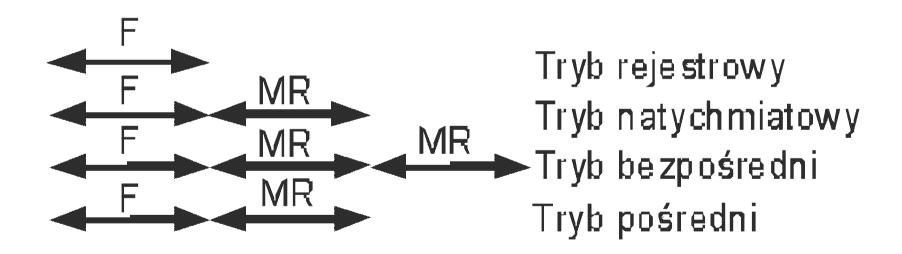

## Cykl maszynowy

### Rodzaje cykli maszynowych

- Pobranie kodu operacyjnego (fetch)

- Odczyt z pamięci (memory read)

- Zapis do pamięci (memory write)

- Odczyt z urządzenia wejściowego (IOread)

- Zapis do urządzenia wyjściowego (IOwrite)

- Cykl przyjęcia przerwania (interrupt)

- Cykl zatrzymania (HALT)

### Cykl instrukcyjny (rozkazowy)

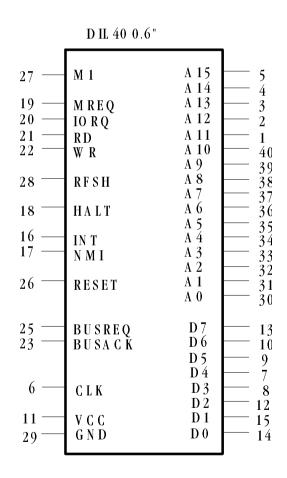

## Końcówki procesora Z-80

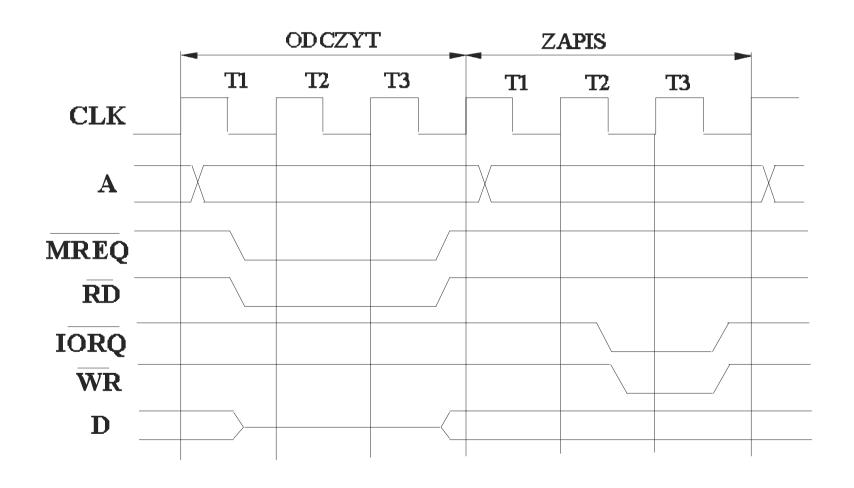

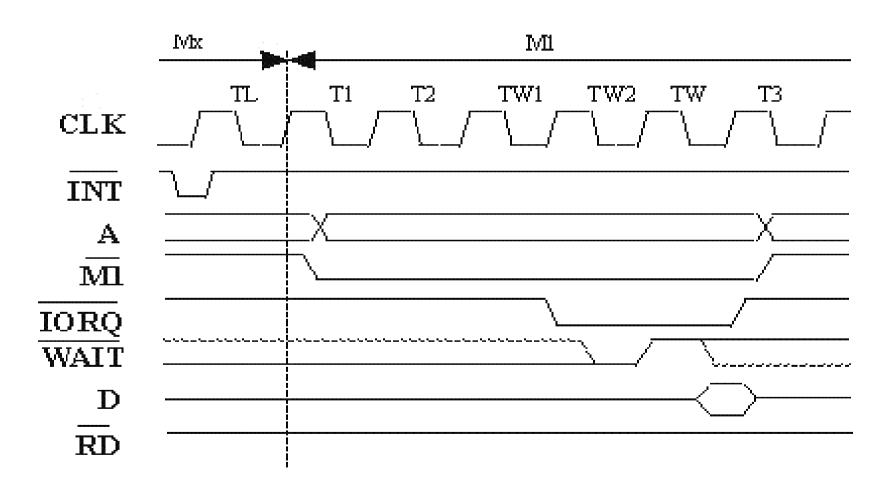

# Cykl odczytu pamięci i zapisu IO

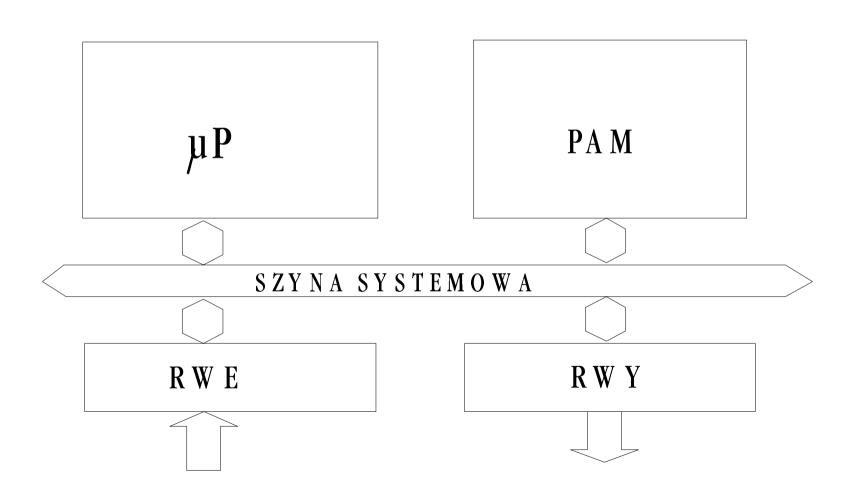

#### Ogólny schemat systemu mikroprocesorowego

# Cykl maszynowy INTA

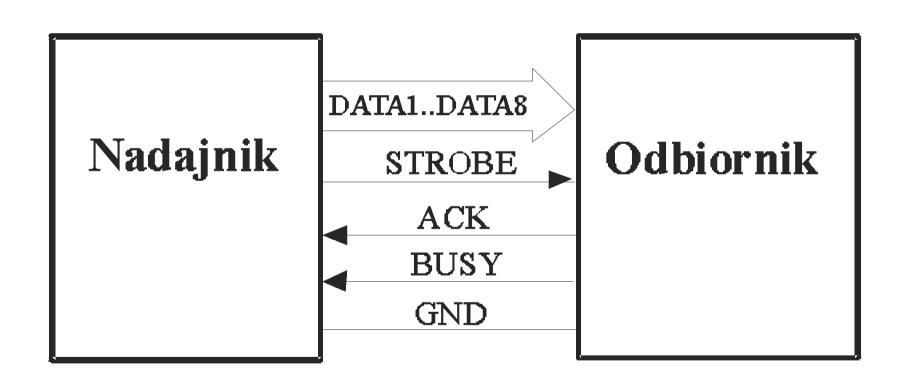

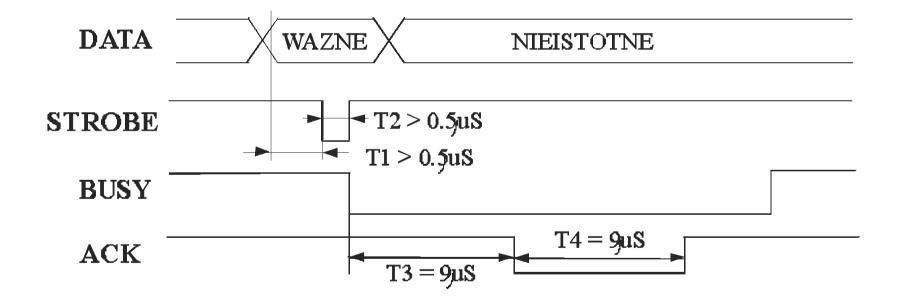

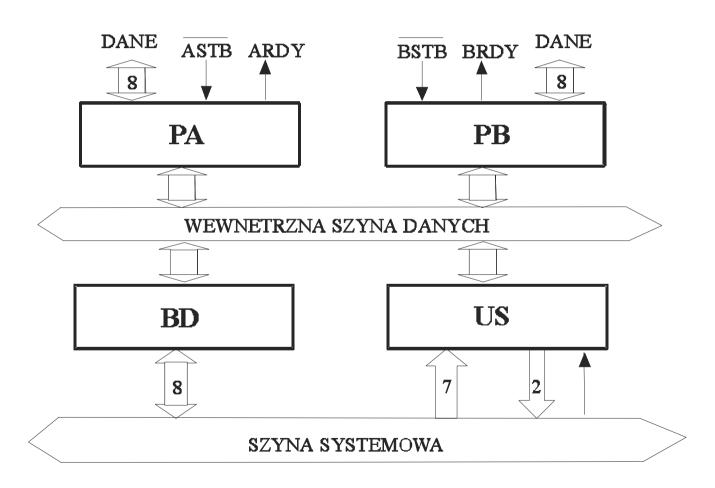

#### Łącze sterownika równoległego z UZ

### Łącze sterownika z UZ

### Łącze sterownika z szyną

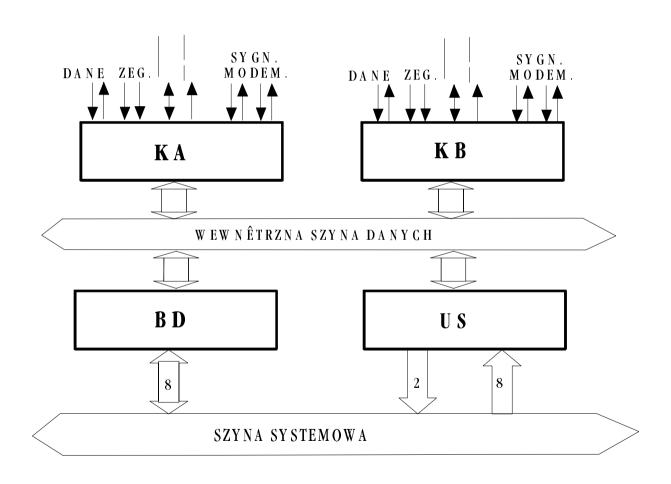

#### Łącze szyny ze sterownikiem szeregowym

### Sygnały łącza modemu

- RTS (ang. Request to send) generuje NAD

- DSR (ang. Data set ready) odbiera ODB

- DTR (ang. Data terminal ready) generuje ODB

- CTS (ang. Clear to send) odbiera NAD

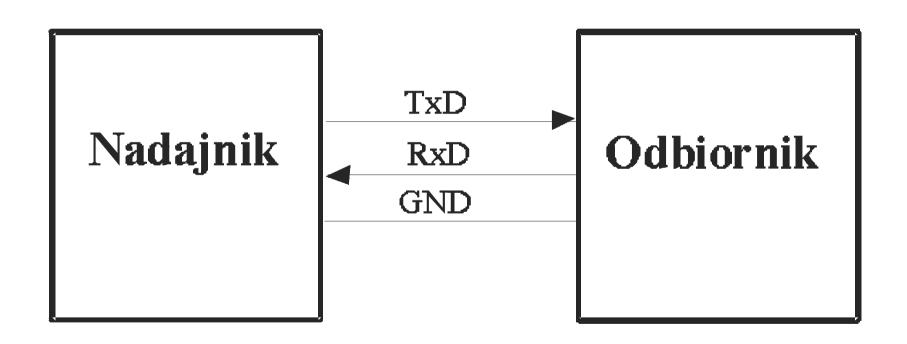

### Łącze sterownika z szeregowym UZ

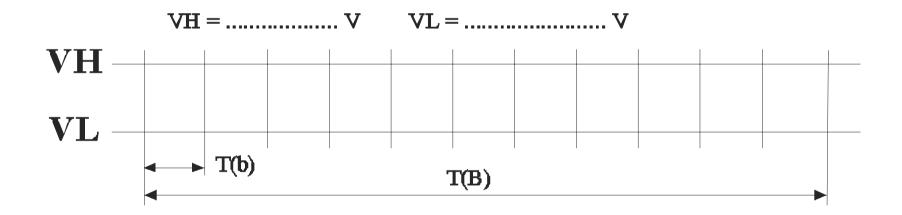

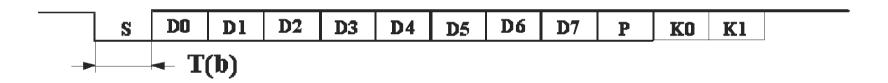

#### Przedziały czasowe w czasie transmisji szeregowej

### Asynchroniczna transmisja szeregowa

### Synchroniczna transmisja szeregowa

Słowo synchronizacji

Pierwszy bajt transmisji

Drugi bajt transmisji

Koniec transmisji - bajty CRC

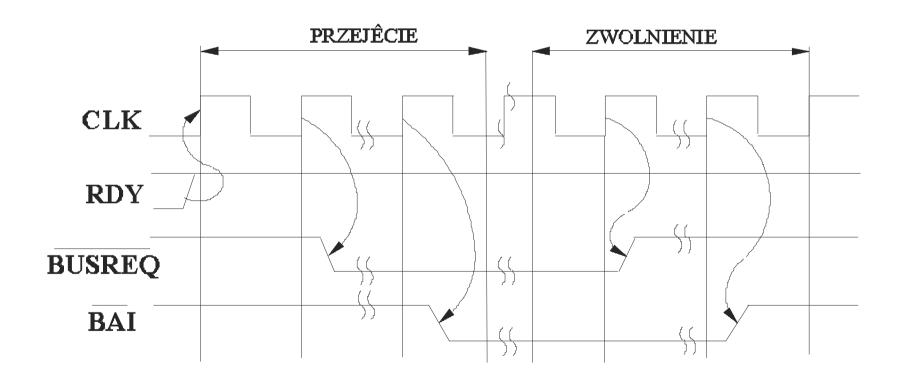

## Dostęp DMA